本篇笔记详细介绍了寄存器及其传输操作的基本概念,包括寄存器的结构、控制信号的作用、寄存器传输语言(RTL)的使用,以及不同类型的寄存器和计数器的设计方法。内容涵盖了并行加载、双向移位、计数器的工作原理及其设计注意事项,最后探讨了基于多路选择器的设计方法和时序电路的设计方法。(由 gpt-4o-mini 生成摘要)

1. 寄存器 Registers

一个 位的寄存器包含 个触发器,还有若干组合电路来实现特定功能,如移位、计数等。

一般通过一个 信号来控制寄存器, 信号一般通过更高阶的电路控制。可以把 信号和 信号的 AND 来作为触发器的控制信号:

- 表示 载入(load),新数据被写入寄存器。

- 表示 储存(store),寄存器保持已经写入的数据。

如果给时钟信号加上一个非门,那么不同触发器的控制信号的时间存在一个非门的延时。 一种解决方案是时钟信号直接接到所有触发器的控制信号上,但触发器的输入信号接一个 2-to-1 MUX,根据控制信号选择是加载触发器的输出,还是从输入流中加载。 时钟偏斜(clock skew)

如果载入操作在同一个时钟脉冲中完成,我们称之是并行(parallel) 的。

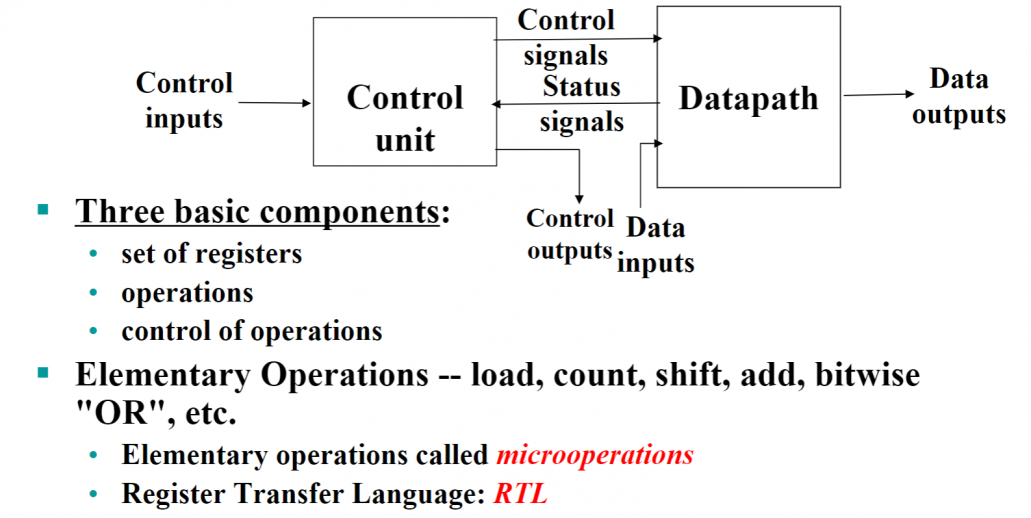

2. 寄存器传输操作 Register Transfer Operations

寄存器传输操作(register transfer operation):处理存储在寄存器中的数据的操作。

微操作(microoperation):关于寄存器传输的初级操作,包括 load/count/shift/add/bitwise OR 等等。

2.1. 寄存器传输语言 Register Transfer Language

寄存器传输语言(register transfer language, RTL) 用来表述寄存器传输操作。

- 字母和数字:表示寄存器

- 小括号:表示位的范围(如

R(1)、PC(7:0)) - 箭头:表示数据的传输(如

R1 <- R2) - 逗号:用于分开多次操作

- 方括号:(可通过寄存器)指定内存地址(如

R0 <- M[AR]) - 条件传输(conditional transfer):如

K1: (R2 <- R1)表示当K1寄存器的值为 1 时执行R2 <- R1。

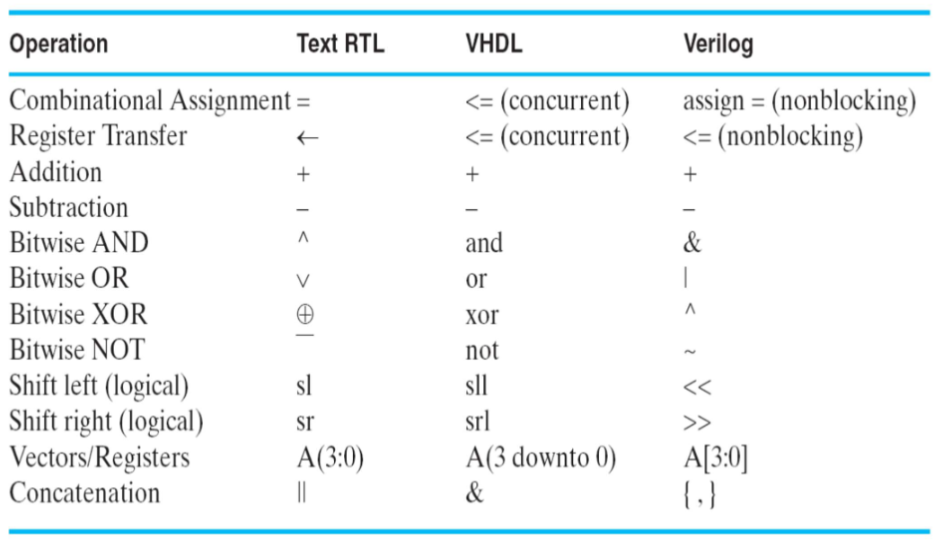

关于寄存器传输操作的硬件描述语言的比较

如用 RTL 来描述一个加减法器的行为( 时加法, 时减法):

2.2. 数据传输结构 Register Transfer Structures

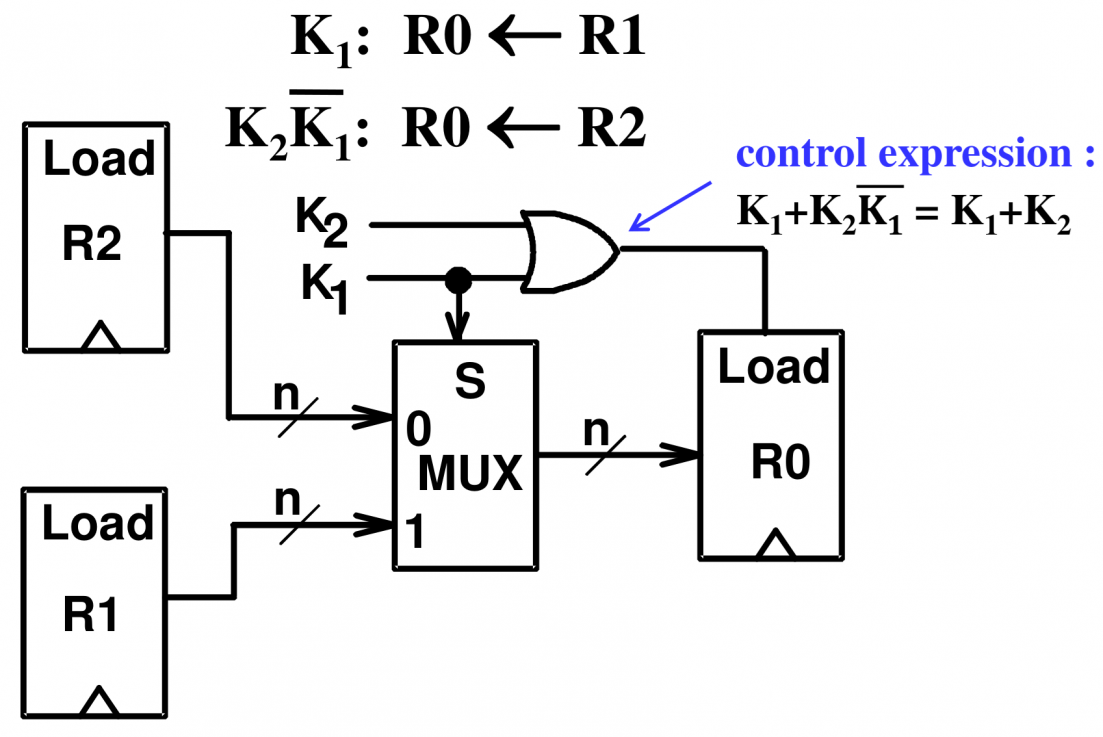

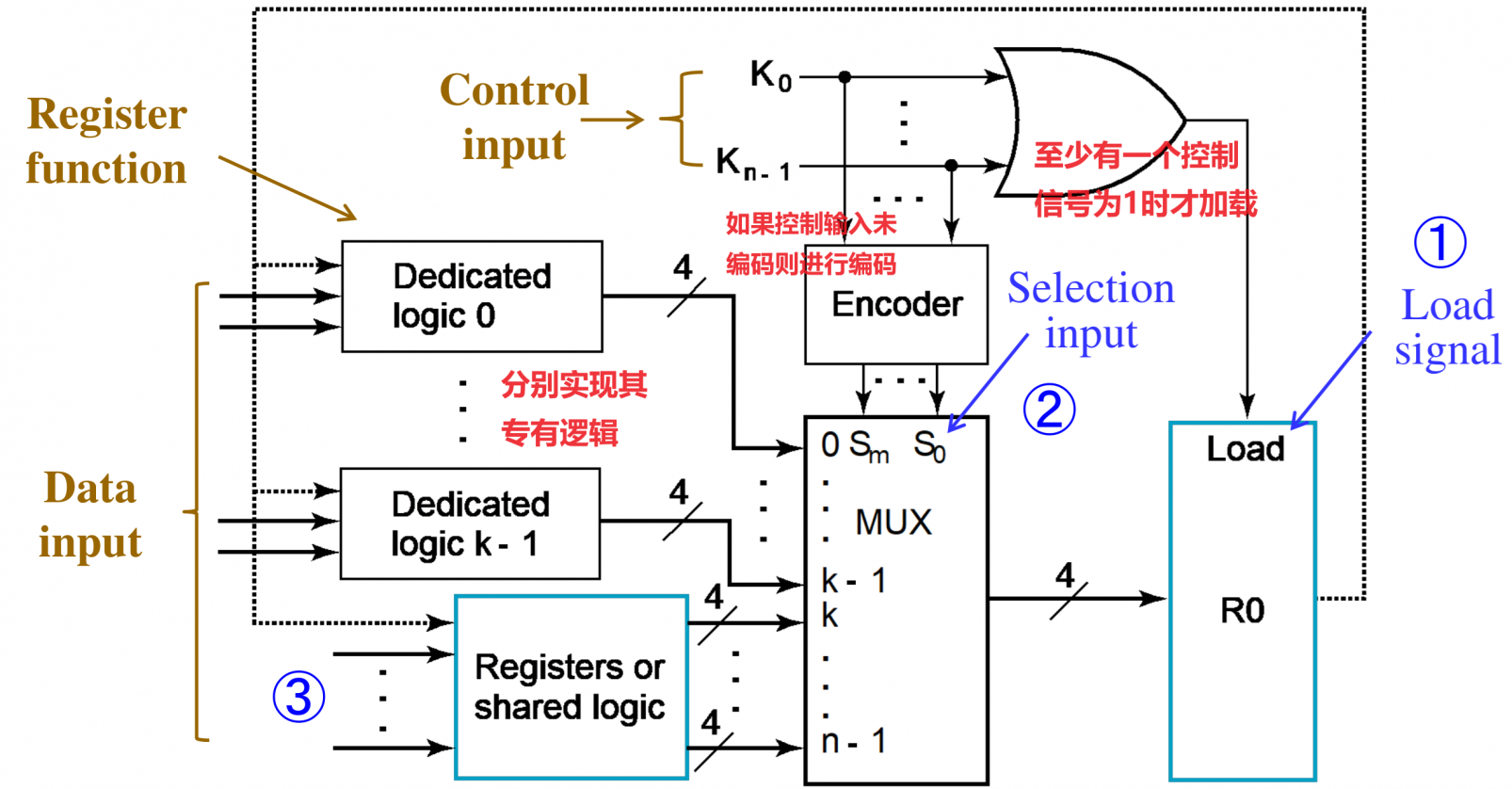

2.2.1. 基于多路选择器的传输 Multiplexer-Based Transfers

多个输入通过一个多路选择器进行选择,从而给到目标寄存器中。

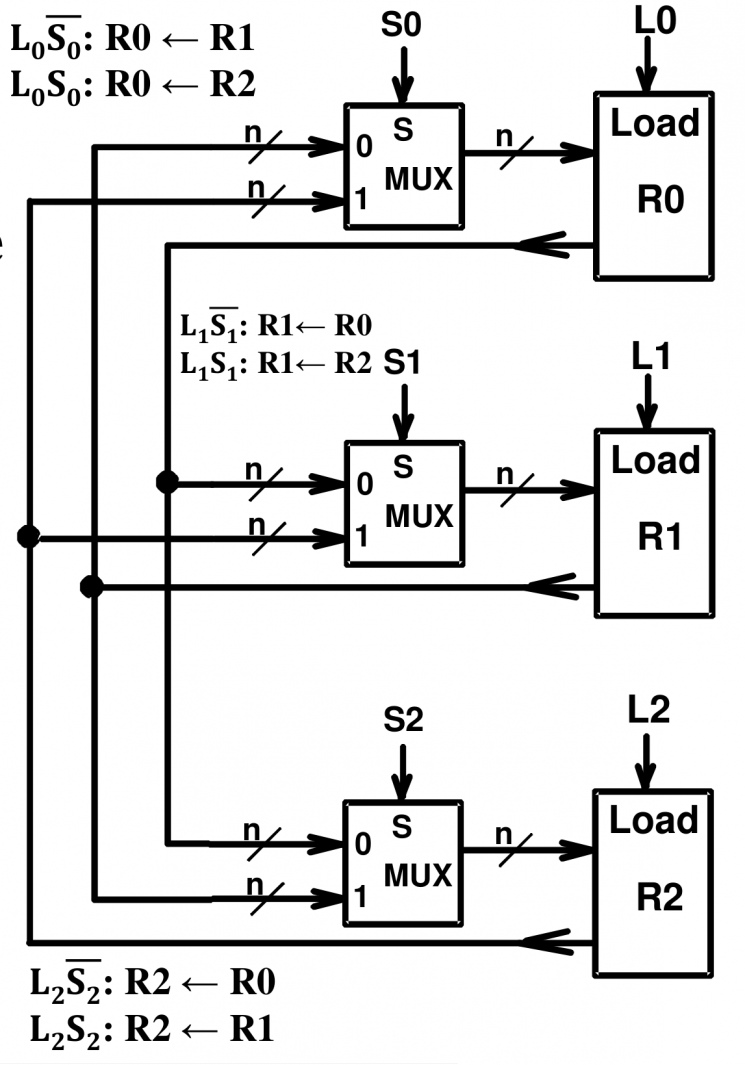

2.2.2. 基于专有的多路选择器的传输 Dedicated MUX-Based Transfers

这里专有的(dedicated) 的 MUX 的意思是说,每个寄存器的输入都通过一个独立的 MUX 进行选择。

- PROS:可以实现在一个时钟节拍中同时的数据传输。

- CONS:门输入代价高。

- GN 的计算:MUX 的反相器是可以共享的,每一个 MUX 里需要两个 2 输入与门和一个 2 输入或门,共 。

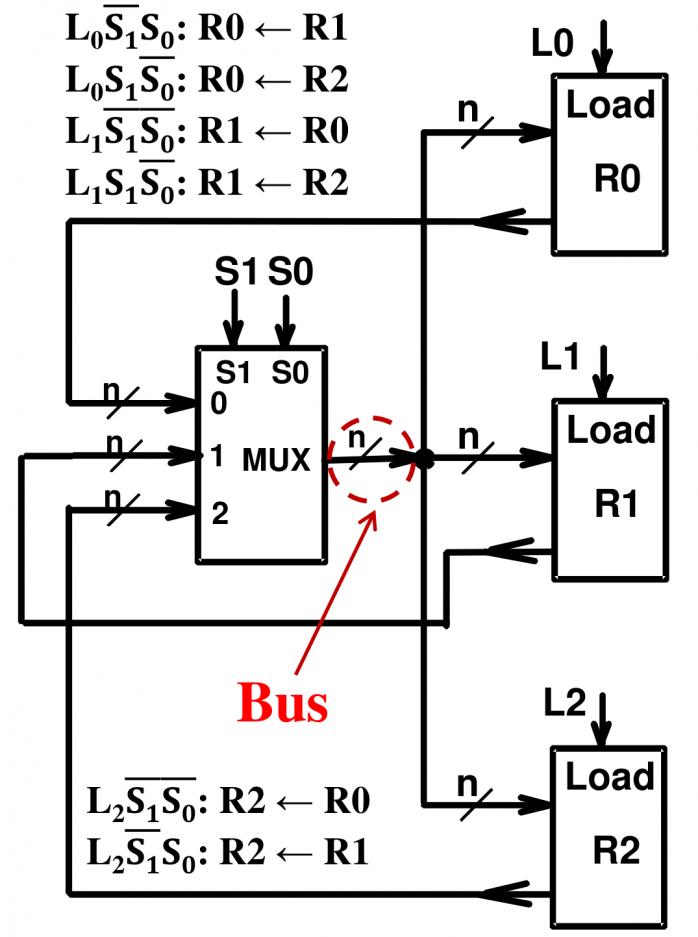

2.2.3. 多路选择器总线 Multiplexer Bus

总线(bus) 的主要思想在于让多个寄存器共享一个多路选择器和数据传输路径,把这个多路选择器称作是共享的(shared)。

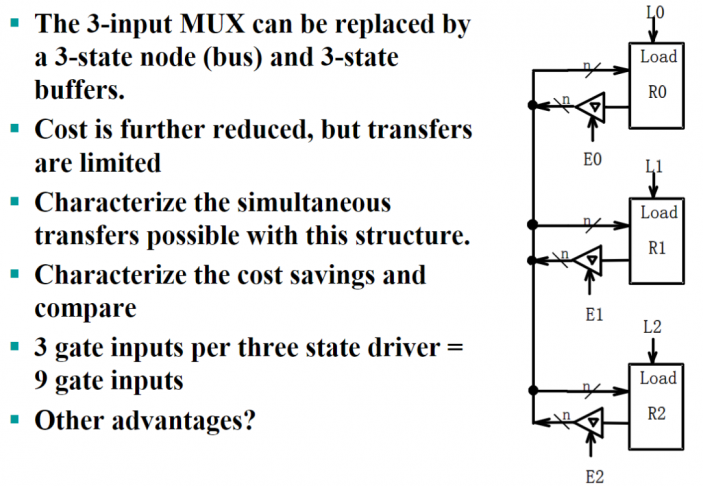

2.2.4. 三态门总线 Three-State Bus

三台总线的实现需要用到三态门(tri-state gate),因为其可以输出高阻态,从而使得来自多个寄存器的输出可以直接连起来而不需要逻辑门或 MUX 的控制。

3. 移位寄存器 Shift Registers

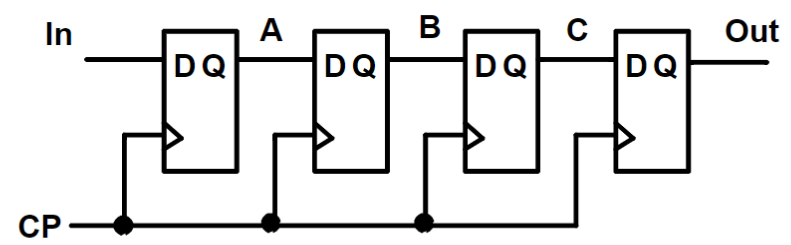

一个普通的移位寄存器(shift register) 如下:

- 串行输入(serial input):。

- 串行输出(serial output):。

- 并行输出(parallel output):、、、。

3.1. 并行加载移位寄存器 Parallel Load Shift Register

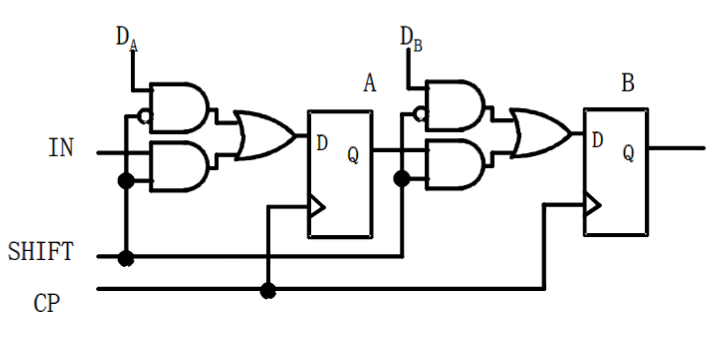

通过给输入信号加一个 2-to-1 MUX 可以实现并行加载功能,这样在 SHIFT 为 0 时,移位寄存器 会直接从 加载数据,并且这一加载过程在同一时间发生(是并行的)。

如果需要支持保持(hold) 功能,可以换成 3-to-1 MUX,并接一路从自己这来的输出,功能表如下:

| Shift | Load | Operation |

|---|---|---|

| 0 | 0 | 保持 no change |

| 0 | 1 | 加载 load |

| 1 | x | 移位 shift down |

注意,实现保持功能时,我们不能直接给时钟信号 CP 加一个与门,这样的话与门的延迟同样会导致上文提到过的时钟歪斜(clock skew) 问题。

3.2. 双向移位寄存器 Bidirectional Shift Registers

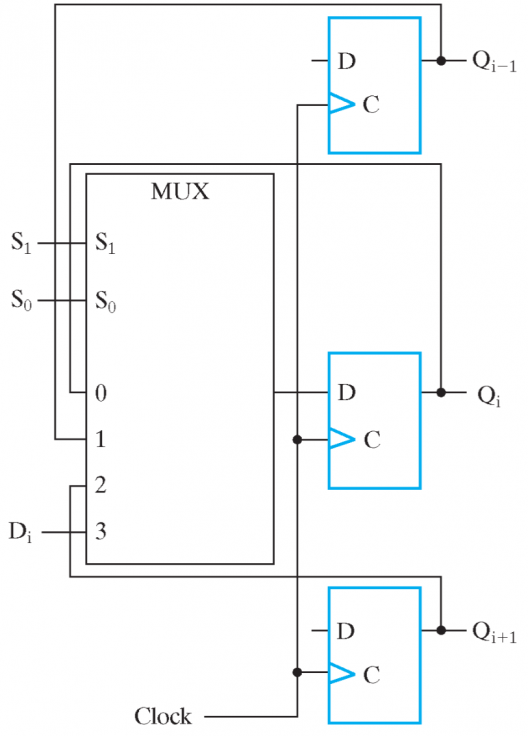

再换用 4-to-1 MUX 可以让我们的移位寄存器同时支持两个方向的移位操作,电路的一部分如下图所示。

其功能表如下( 为控制信号):

| Operation | ||

|---|---|---|

| 0 | 0 | 保持 no change |

| 0 | 1 | 向下移位 shift down |

| 1 | 0 | 向上移位 shift up |

| 1 | 1 | 平行加载 parallel load |

如果需要让移位寄存器支持更多功能,更换 MUX 并设计相应电路即可。

4. 计数器 Counters

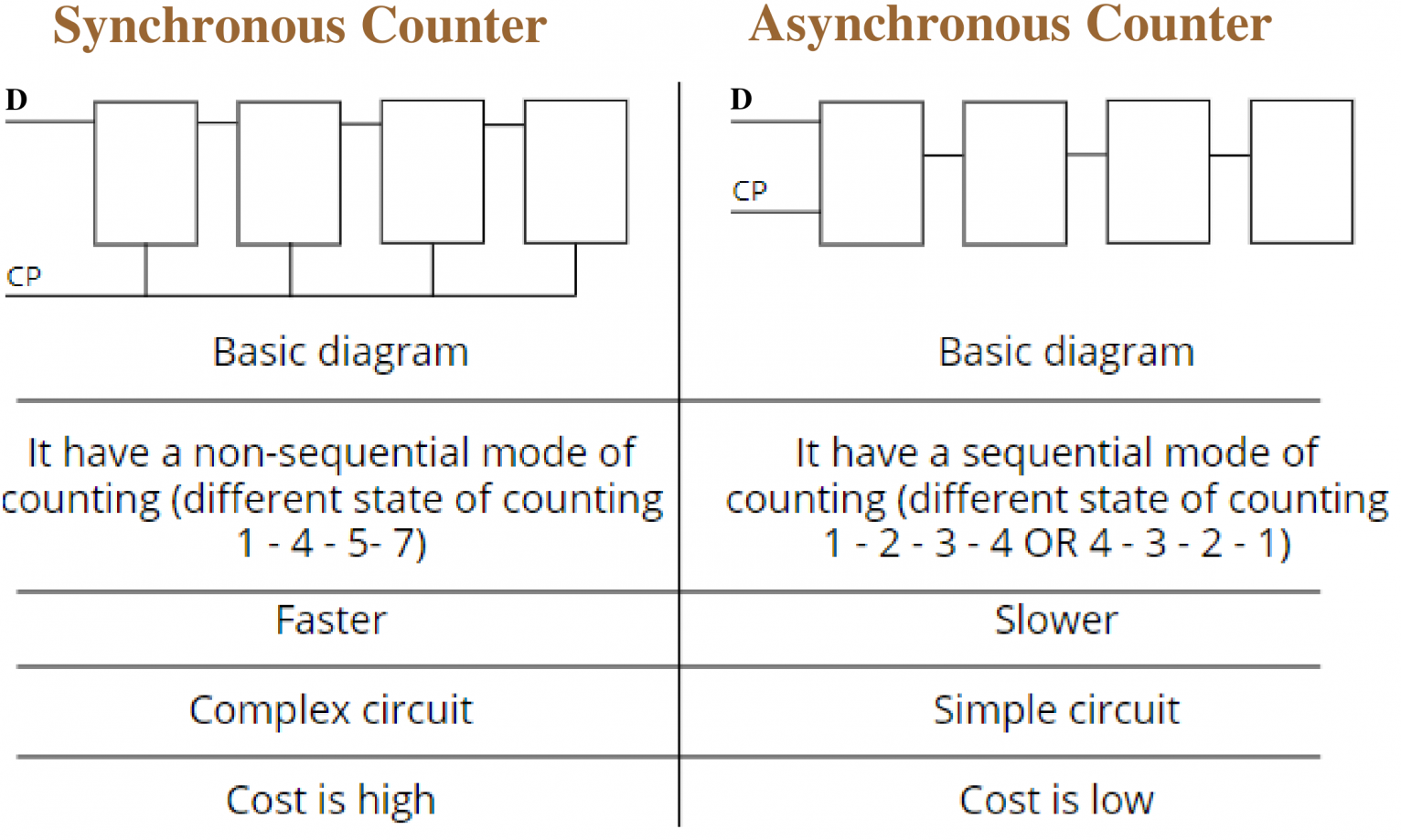

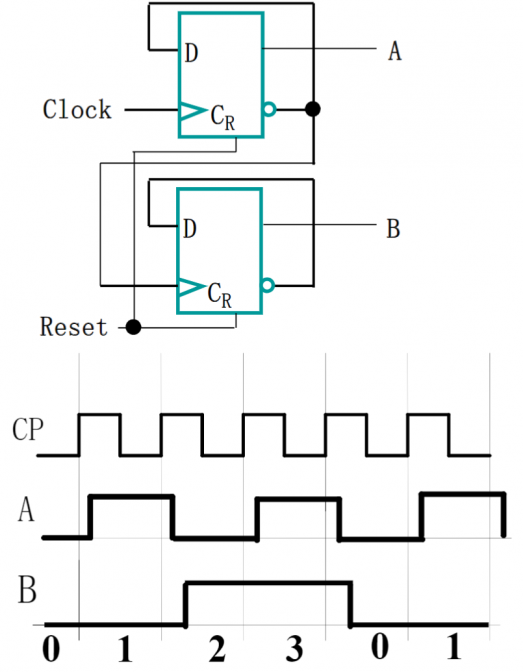

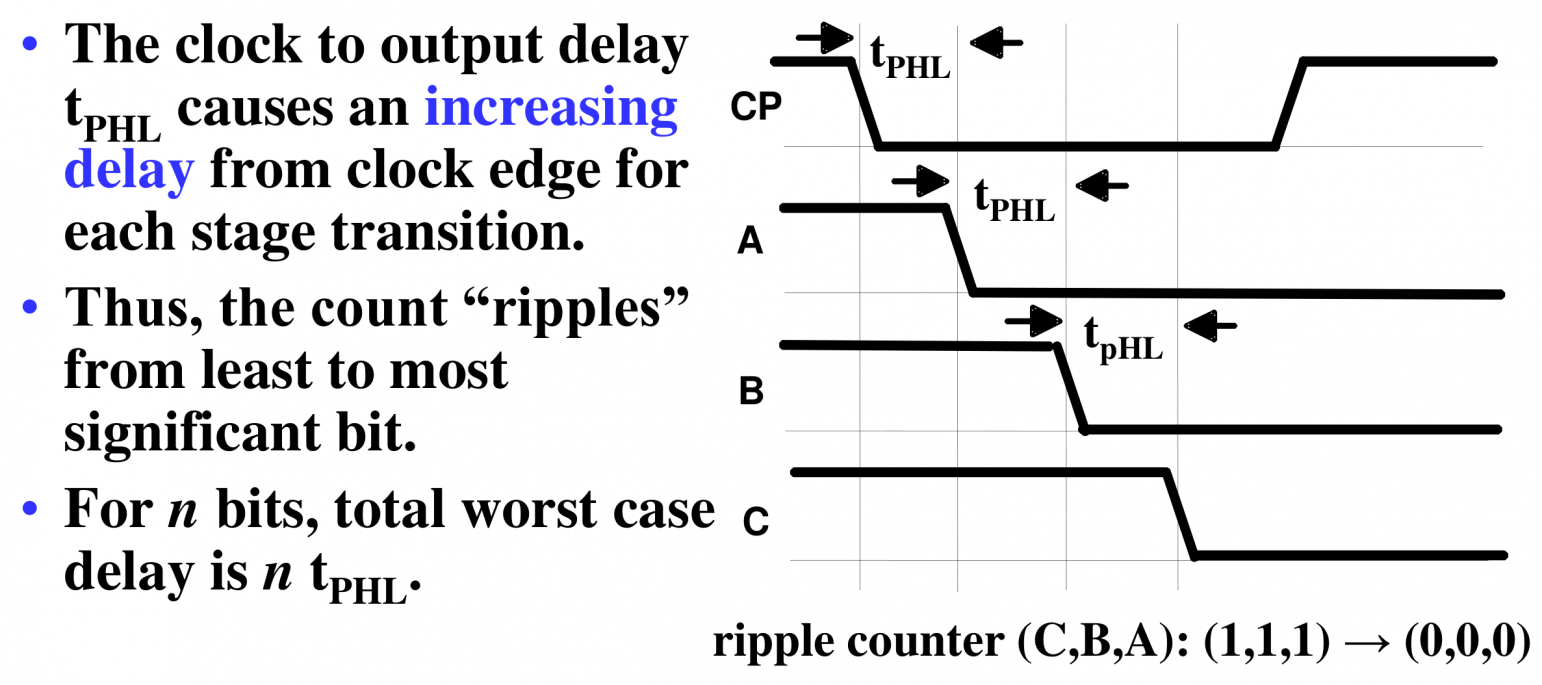

4.1. 纹波计数器 Ripple Counter

触发器 把时钟信号作为控制信号 ,其反转频率是时钟信号的一半; 把 的输出作为控制信号,其反转频率是 的一半,是时钟信号的四分之一。从而实现计数器的功能。

- 最低有效位(LSB)

- 最高有效位(MSB)

从最低有效位开始计数,低位触发器的输出作为更高一位触发器的控制信号。

时延计算:分析是上升沿还是下降沿,或者直接 。

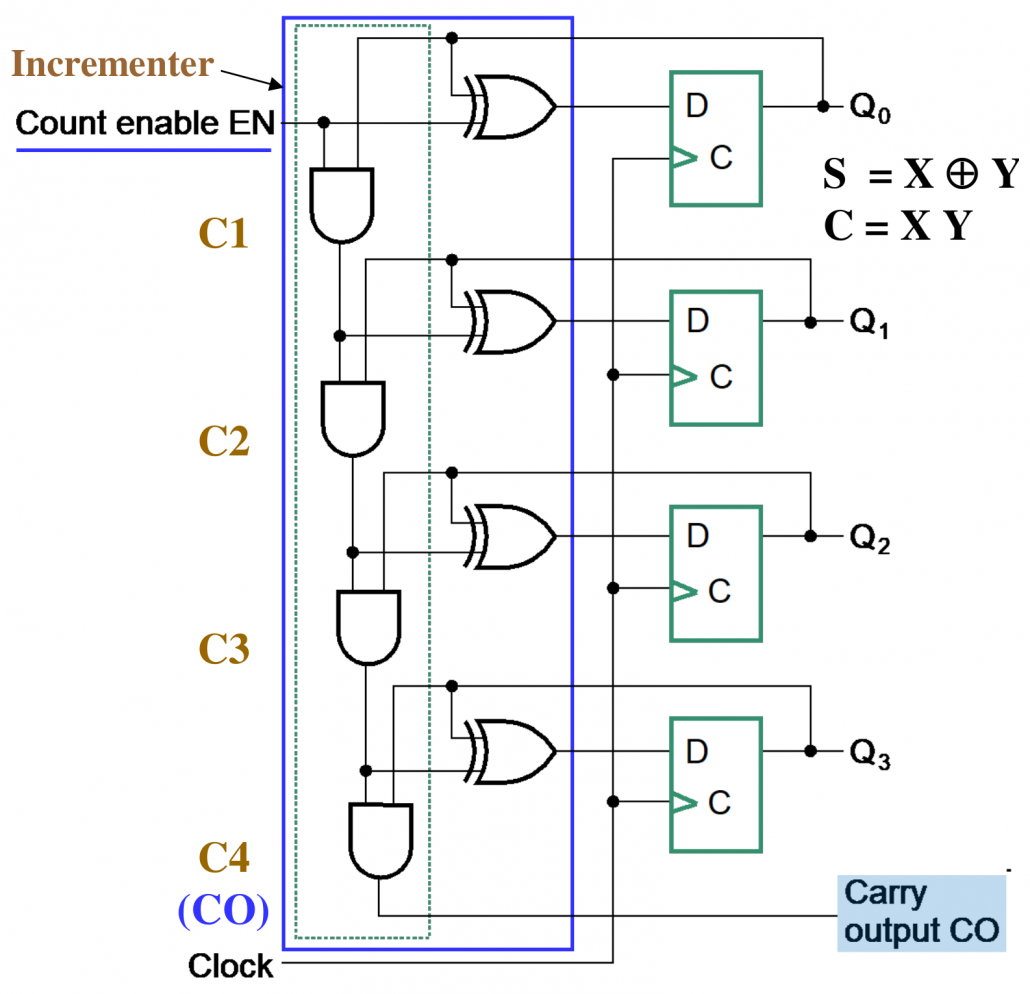

4.2. 同步计数器 Synchronous Counters

触发器只用来保存状态,计数的功能用组合电路( 位计数器只需要 个半加器)实现。所有触发器同步改变。

- 计数使能(count enable = CE):控制是否进行计数,当 且边沿到来时进行一次计数,当 时处于保持状态。

- 进位输出(carry output = CO):给出最高的进位作为输出,可以指示计数器是否达到上界。

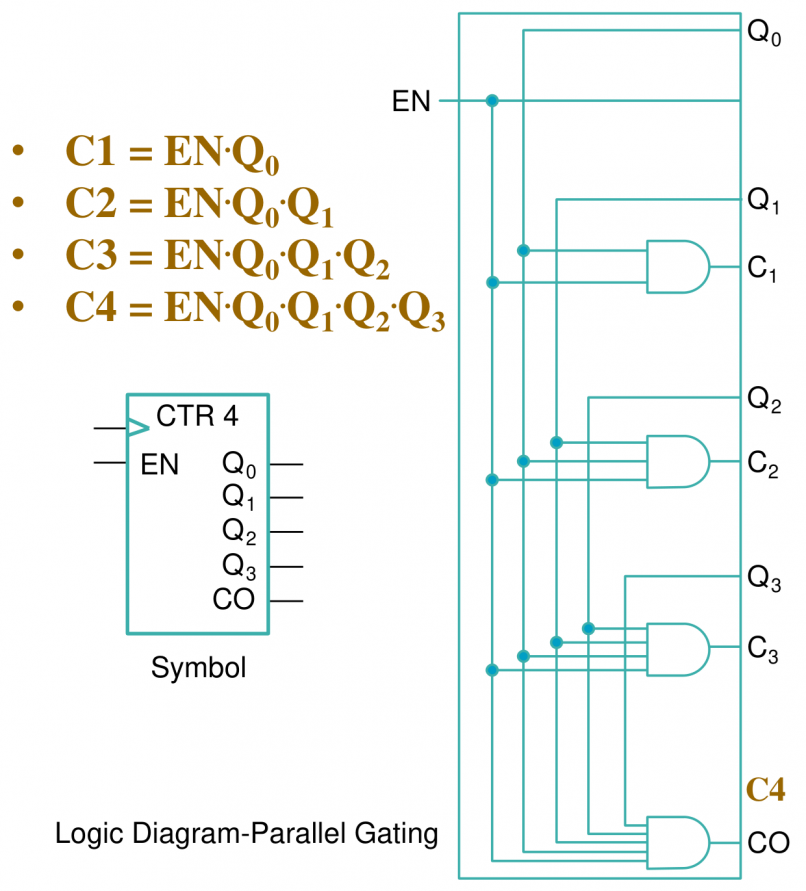

类似于加法器,我们也可以在并行计数器中实现提前进位:

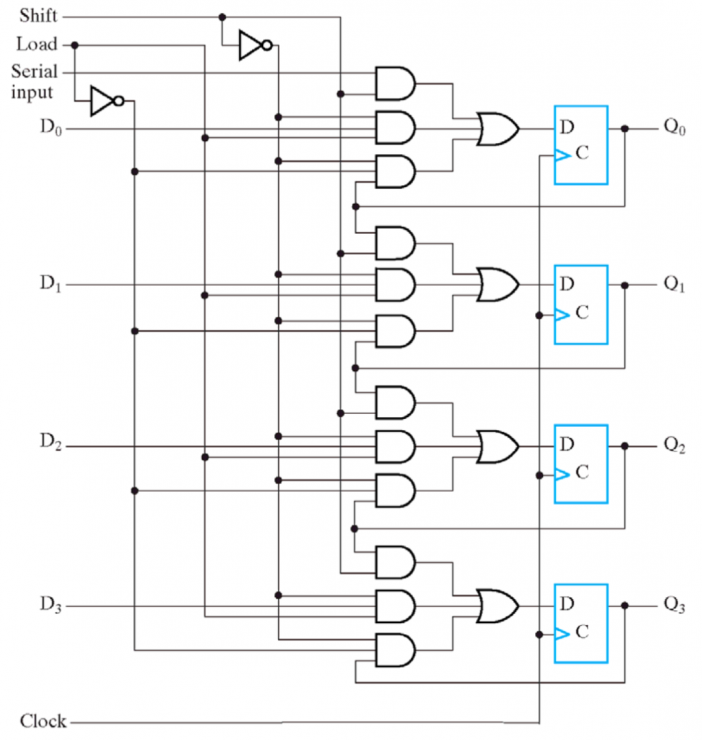

4.3. 支持平行加载的计数器 Counter with Parallel Load

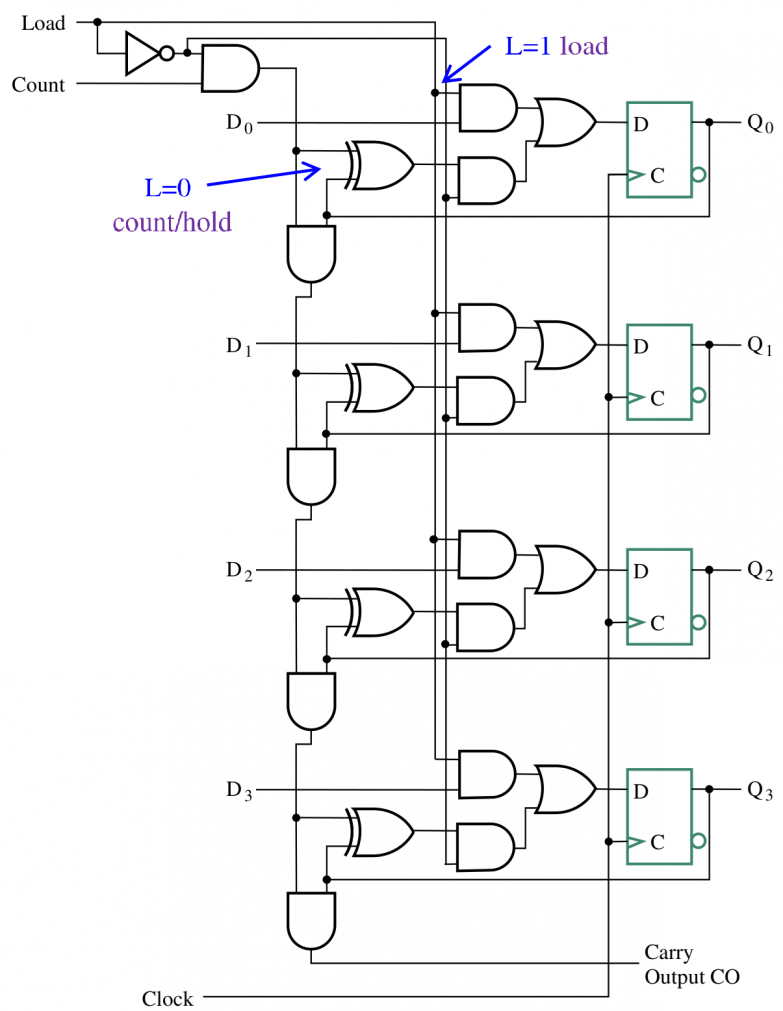

通过一个 2-to-1 MUX 控制是从 中并行加载还是从组合逻辑中加载。

4.4. 模 N 的计数器 Counting Modulo N

我们以设计模 10 的计数器(BCD 计数器为例),那么只有 到 是有效的(valid),剩下的 6 个状态都是未使用的状态。

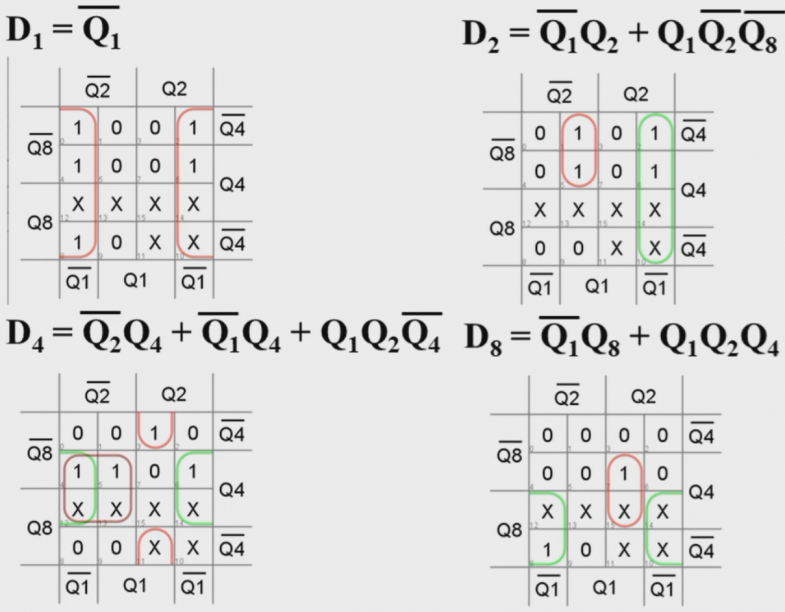

写出状态转移的激励方程,并通过卡诺图化简,可以得到我们需要的组合逻辑。

需要注意的是,虽然剩余 6 个状态是未使用状态,但是如果计数器因为意外处于未使用状态时,他的下一状态是确定的,画图可知我们设计的这一计数器在有限步后又会回到有效状态(称为自恢复能力;并非对于所有计数器都成立后,最好设计成这样的)。我们也可以设计一个 输出,用于指示是否进入了未使用状态,同样可用卡诺图进行化简。

不推荐的设计(自杀式计数器):让模 的计数器在输出变成 时直接给所有寄存器异步清零。如果异步清零过程的时延不同,可能“卡在”中间的任意有效状态,非常不稳定。

5. 寄存器单元设计

5.1. 基于 MUX 的设计方法 Multiplexer Approach

-

寄存器功能(register functions):可以通过寄存器传输语言 RTL 来描述。

-

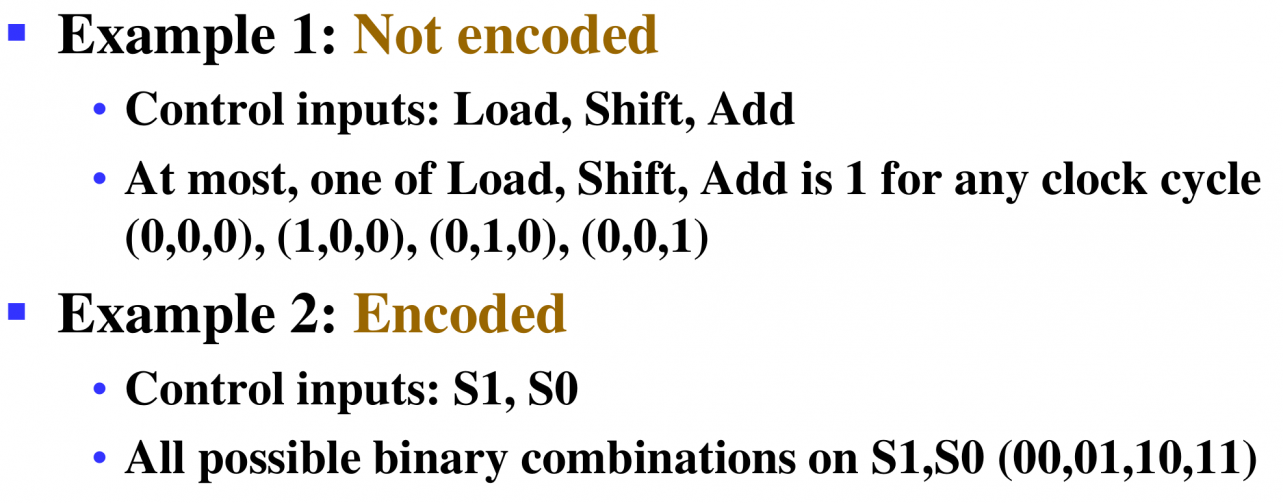

控制输入(control inputs):输入控制信号,控制信号的可以是编码的(encoded) 或未编码的。

- 数据输入(date inputs):从寄存器中输入。

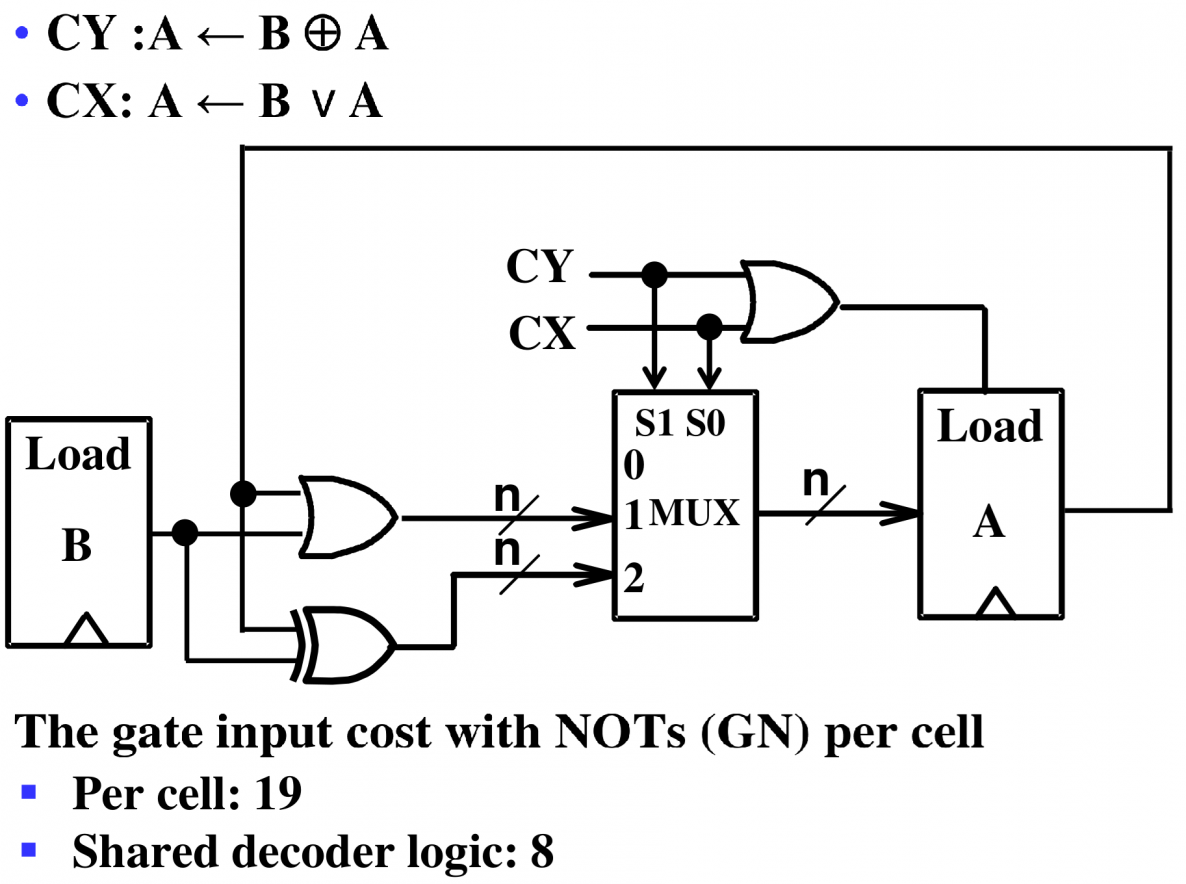

Example

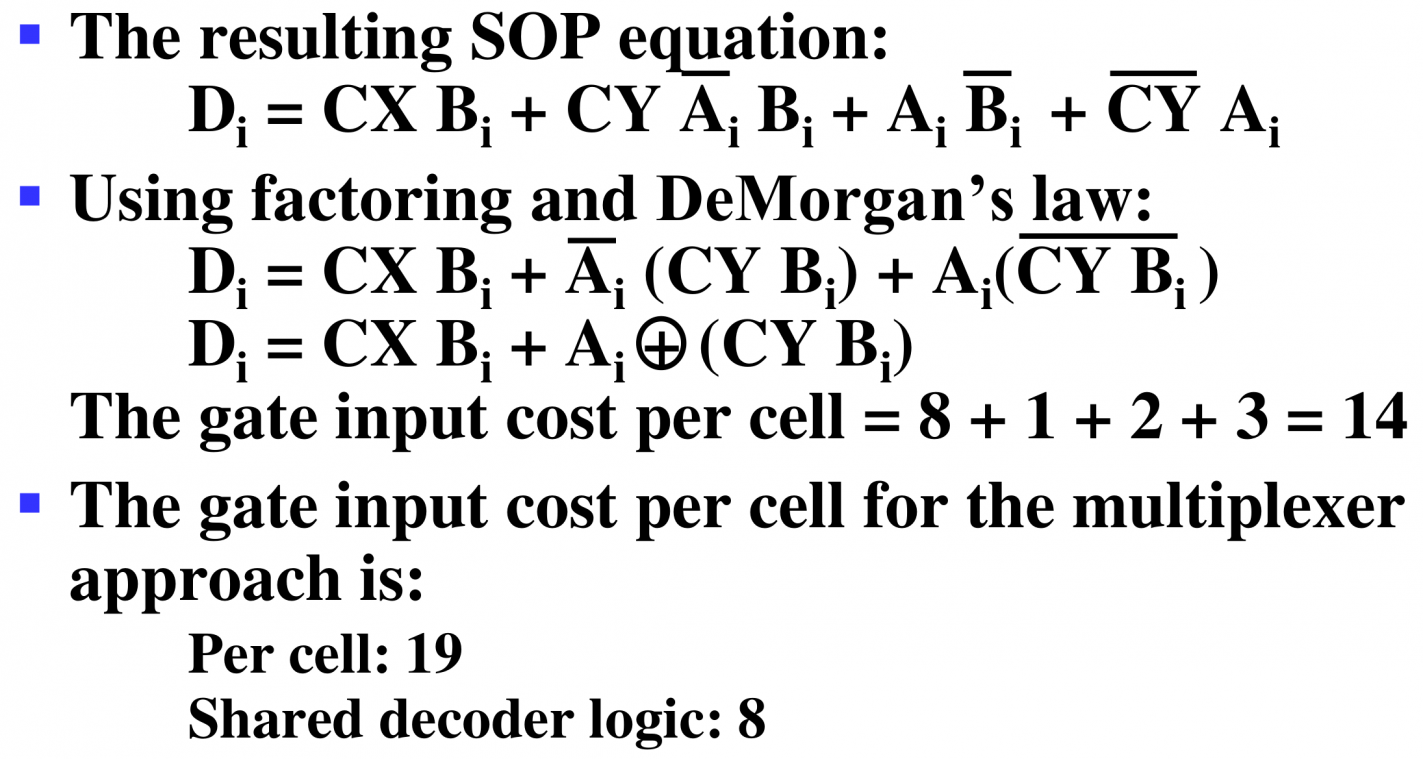

5.2. 基于时序电路的设计方法 Sequential Circuit Design Approach

这里状态本身就是输出,所以一定是摩尔型电路。使用时序电路的相关方法进行设计,虽然结果更优但设计过程非常麻烦。

Example